# Isolated Boost PFC Preregulator Controller

#### **FEATURES**

- PFC With Isolation, V<sub>O</sub> < V<sub>IN</sub>

- Single Power Stage

- Zero Current Switched IGBT

- Programmable ZCS Time

- Corrects PF to >0.99

- Fixed Frequency, Average Current Control

- Improved RMS Feedforward

- Soft Start

- 9V to 18V Supply V Range

- 20-Pin DW, N, J, and L Packages

#### **DESCRIPTION**

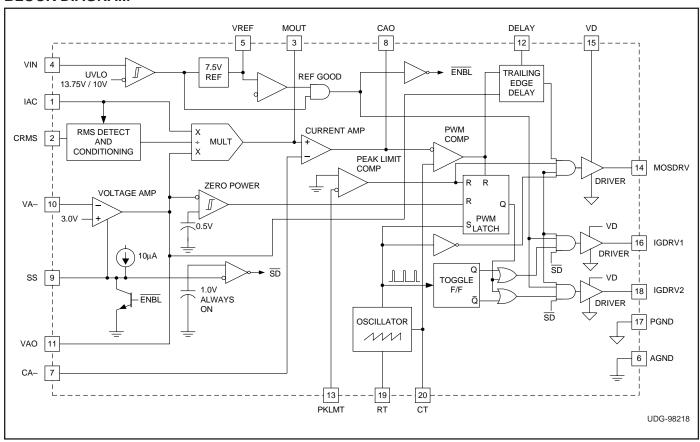

The UCC3857 provides all of the control functions necessary for an Isolated Boost PFC Converter. These converters have the advantage of transformer isolation between primary and secondary, as well as an output bus voltage that is lower than the input voltage. By providing both power factor correction and down conversion in a single power processing stage, the UCC3857 is ideal for applications which require high efficiency, integration, and performance.

The UCC3857 brings together the control functions and drivers necessary to generate overlapping drive signals for external IGBT switches, and provides a separate output to drive an external power MOSFET which provides zero current switching (ZCS) for both the IGBTs. Full programmability is provided for the MOSFET driver delay time with an external RC network. ZCS for the IGBT switches alleviates the undesirable turn off losses typically associated with these devices. This allows for higher switching frequencies, smaller magnetic components and higher efficiency. The power factor correction (PFC) portion of the UCC3857 employs the familiar average current control scheme used in previous Unitrode controllers. Internal circuitry changes, however, have simplified the design of the PFC section and improved performance.

(continued)

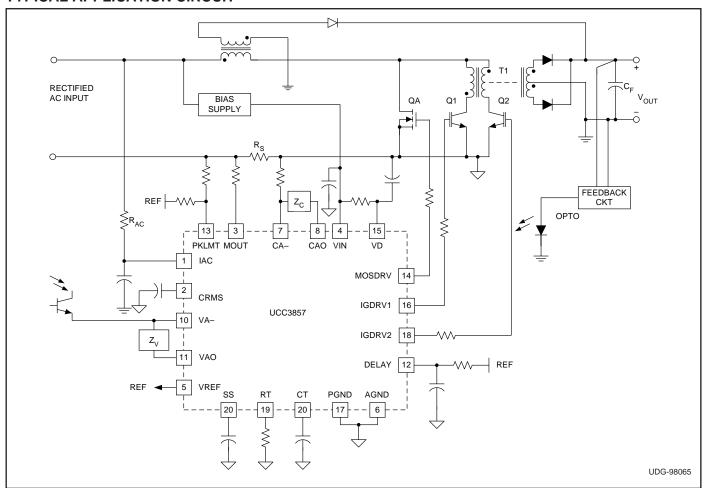

#### TYPICAL APPLICATION CIRCUIT

#### **ABSOLUTE MAXIMUM RATINGS**

| Input Supply Voltage (VIN, VD)              |

|---------------------------------------------|

| (CRMS, MOUT, CA-, VA-, CT, RT, PKLMT)       |

| (Maximum Forced Voltage)0.3V to 5V          |

| IAC (Maximum Forced Current) 300μA          |

| Reference Output Current Internally Limited |

| Output Current (MOSDRV, IGDRV1, IGDRV2)     |

| Pulsed                                      |

| Continuous                                  |

| Storage Temperature65°C to +150°C           |

| Junction Temperature55°C to +150°C          |

| Lead Temperature (Soldering, 10 Sec.)+300°C |

Unless otherwise indicated, voltages are reference to ground and currents are positive into, negative out of the specified terminal. Pulsed is defined as a less than 10% duty cycle with a maximum duration of 500 s. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

## **DESCRIPTION** (continued)

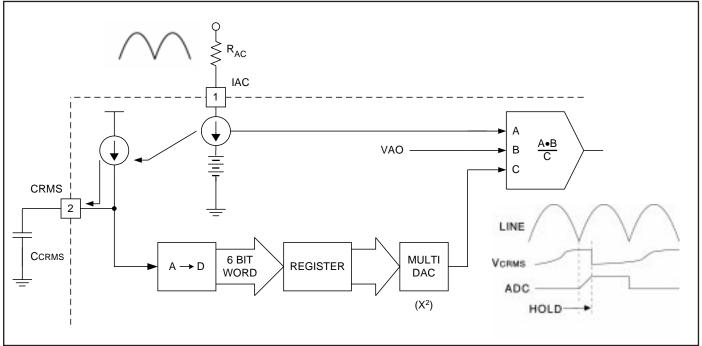

Controller improvements include an internal 6 bit A-D converter for RMS input line voltage detection, a zero load power circuit, and significantly lower quiescent operating current. The A-D converter eliminates an external 2 pole low pass filter for RMS detection.

This simplifies the converter design, eliminates 2nd harmonic ripple from the feedforward component, and provides an approximate 6 times improvement in input line transient response. The zero load power comparator prevents energy transfer during open load conditions without compromising power factor at light loads. Low startup and operating currents which are achieved through the use of Unitrode's BCDMOS process simplify the auxiliary bootstrap supply design.

Additional features include: under voltage lockout for reliable off-line startup, a programmable over current shutdown, an auxiliary shutdown port, a precision 7.5V reference, a high amplitude oscillator ramp for improved noise immunity, softstart, and a low offset analog square, multiple and divide circuit. Like previous Unitrode PFC controllers, worldwide operation without range switches is easily implemented.

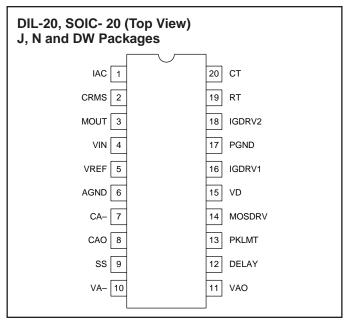

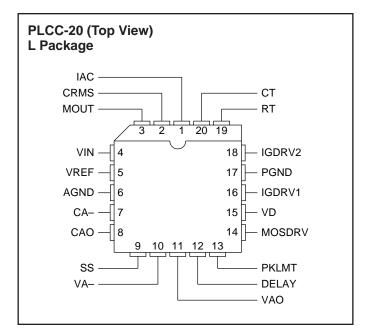

#### **CONNECTION DIAGRAMS**

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for  $T_A = 0^{\circ}C$  to  $70^{\circ}C$  for the UCC3857,  $-40^{\circ}C$  to  $+85^{\circ}C$  for the UCC2857, and  $-55^{\circ}C$  to  $+125^{\circ}C$  for the UCC1857,  $V_{VIN}$ ,  $V_{VD} = 12V$ ,  $R_T = 19.2K$ ,  $C_T = 680pF$ .  $T_A = T_J$ .

| PARAMETER                           | TEST CONDITIONS                                                             | MIN      | TYP   | MAX   | UNITS |

|-------------------------------------|-----------------------------------------------------------------------------|----------|-------|-------|-------|

| Input Supply                        |                                                                             |          |       |       |       |

| Supply Current, Active              | No Load on Outputs, V <sub>VD</sub> = V <sub>VIN</sub>                      |          | 3.5   | 5     | mA    |

| Supply Current, Startup             | No Load on Outputs, V <sub>VD</sub> = V <sub>VIN</sub>                      |          | 60    | TBD   | μΑ    |

| VIN UVLO Threshold                  |                                                                             |          | 13.75 | 15.5  | V     |

| UVLO Threshold Hysteresis           |                                                                             | 3        | 3.75  | TBD   | V     |

| Reference                           |                                                                             |          |       |       |       |

| Output Voltage (V <sub>VREF</sub> ) | $T_J = 25$ °C, $I_{REF} = 1$ mA                                             | 7.387    | 7.5   | 7.613 | V     |

|                                     | Over Temperature, UCC3857                                                   | 7.368    | 7.5   | 7.631 | V     |

|                                     | Over Temperature, UCC1857, UCC2857                                          | 7.313    | 7.5   | 7.687 | V     |

| Load Regulation                     | I <sub>REF</sub> = 1mA to 10mA                                              |          | 2     | 10    | mV    |

| Line Regulation                     | $V_{VIN} = V_{VD} = 12V$ to 16V                                             |          | 2     | 15    | mV    |

| Short Circuit Current               | $V_{VREF} = 0V$                                                             |          | -55   | -30   | mA    |

| Current Amplifier                   |                                                                             |          |       |       |       |

| Input Offset Voltage                | (Note 1)                                                                    | -3       | 0     | 3     | mV    |

| Input Bias Current                  | (Note 1)                                                                    |          | -50   |       | nA    |

| Input Offset Current                | (Note 1)                                                                    |          | 25    |       | nA    |

| CMRR                                | $V_{CM} = 0V \text{ to } 1.5V, V_{CAO} = 3V$                                |          | 80    |       | dB    |

| AVOL                                | $V_{CM} = 0V$ , $V_{CAO} = 2V$ to $5V$                                      | 65       | 85    |       | dB    |

| VOH                                 | Load on CAO = $50\mu$ A, $V_{MOUT} = 1V$ , $V_{CA-} = 0V$                   | 6        | 7     |       | V     |

| VOL                                 | Load on CAO = 50μA, V <sub>MOUT</sub> = 0V, VCA- = 1V                       |          | 0.2   |       | V     |

| Maximum Output Current              | Source: V <sub>CA</sub> = 0V, V <sub>MOUT</sub> = 1V, V <sub>CAO</sub> = 3V |          | -150  |       | μΑ    |

|                                     | Sink: $V_{CA-} = 1V$ , $V_{MOUT} = 0V$ , $V_{CAO} = 3V$                     | 5        | 30    | 50    | mA    |

| Gain Bandwidth Product              | f <sub>IN</sub> = 100kHz, 10mV p – p                                        | 3        | 5     |       | MHz   |

| Voltage Amplifier                   |                                                                             |          |       |       | •     |

| Input Voltage                       | Measured on $V_{VA-}$ , $V_{VAO} = 3V$                                      | 2.9      | 3     | 3.1   | V     |

| Input Bias Current                  | Measured on $V_{VA-}$ , $V_{VAO} = 3V$                                      |          | -50   |       | nA    |

| AVOL                                | $V_{VAO} = 1V$ to 5V                                                        |          | 75    |       | dB    |

| VOH                                 | Load on $V_{VAO}$ = -50 $\mu$ A, $V_{VA}$ = 2.8 $V$                         | 5.3      | 5.55  | 5.7   | V     |

| VOL                                 | Load on $V_{VAO}$ = 50 $\mu$ A, $V_{VA-}$ = 3.2 $V$                         |          | 0.1   | 0.45  | V     |

| Maximum Output Current              | Source: V <sub>VA</sub> = 2.8V, V <sub>VAO</sub> = 3V                       | -20      | -12   | -5    | mA    |

|                                     | Sink: $V_{VA-} = 3.2V$ , $V_{VAO} = 3V$                                     | 5        | 20    | 30    | mA    |

| Oscillator                          |                                                                             | <u>.</u> |       | •     |       |

| Initial Accuracy                    | T <sub>J</sub> = 25°C                                                       | 42.5     | 50    | 57.5  | kHz   |

|                                     |                                                                             | 40       | 50    | 60    | kHz   |

| Voltage Stability                   | V <sub>VIN</sub> = 12V to 18V                                               |          | 1     |       | %     |

| CT Ramp Peak-Valley Amplitude       |                                                                             | 4        | 4.5   | 5     | V     |

| CT Ramp Valley Voltage              |                                                                             |          | 1.5   |       | V     |

| Output Drivers                      |                                                                             |          |       |       |       |

| VOH                                 | IL = -100mA                                                                 | 9        | 10    |       | V     |

| VOL                                 | IL = 100mA                                                                  |          | 0.1   | 0.5   | V     |

| Rise Time                           | $C_{LOAD} = 1nF$                                                            |          | 25    | TBD   | ns    |

| Fall Time                           | $C_{LOAD} = 1nF$                                                            |          | 10    | TBD   | ns    |

| Trailing Edge Delay                 |                                                                             |          |       |       | -     |

| Delay Time                          | $R_D = 12k, C_D = 200pF, V_{VAO} = 4V$                                      | 1.6      | 2     | 2.4   | μs    |

**ELECTRICAL CHARACTERISTICS:** Unless otherwise stated, these specifications apply for  $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  for the UCC3857,  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  for the UCC2857, and  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for the UCC1857,  $V_{VIN}$ ,  $V_{VD} = 12\text{V}$ ,  $R_T = 19.2\text{K}$ ,  $C_T = 680\text{pF}$ .  $T_A = T_J$ .

| · A · 0·                                   |                                                             |     |      |     |       |

|--------------------------------------------|-------------------------------------------------------------|-----|------|-----|-------|

| PARAMETER                                  | TEST CONDITIONS                                             | MIN | TYP  | MAX | UNITS |

| Soft Start                                 |                                                             |     |      |     |       |

| Charge Current                             |                                                             |     | 10   |     | μΑ    |

| Shutdown Comparator Threshold              | Measured on SS                                              | 0   |      | 0.4 | V     |

| Multiplier                                 |                                                             | _   |      |     | _     |

| Output Current, IAC Limited                | $I_{AC} = 100\mu A, V_{VAO} = 5.5V, V_{CRMS} = 0V$          |     | -200 |     | μΑ    |

| Output Current, Power Limited              | $I_{AC} = 100 \mu A$ , $V_{VAO} = 5.5 V$ , $V_{CRMS} = 1 V$ |     | -200 |     | μΑ    |

| Output Current, Zero                       | $I_{AC} = 0$                                                | -2  | 0    | 2   | μΑ    |

| Gain Constant                              |                                                             |     | 2.5  |     | 1/V   |

| Zero Power, Peak Current                   |                                                             |     |      |     |       |

| Zero Power Comparator Threshold            | Measured on VAO                                             |     | 0.5  |     | V     |

| Peak Current Limit Comparator<br>Threshold | Measured on PKLMT                                           |     | 0    |     | V     |

Note 1: Common mode voltages = 0V,  $V_{CAO} = 3V$

#### PIN DESCRIPTIONS

**AGND:** Reference point of the internal reference and all thresholds, as well as the return for the remainder of the device except for the output drivers.

**CA-:** Inverting input of the inner current loop error amplifier.

**CAO:** Output of the inner current loop error amplifier. This output can swing between approximately 0.2V and 6V. It is one of the inputs to the PWM comparator.

VAO: This is the output of the voltage loop error amplifier. It is internally clamped to approximately 5.6V by the UCC3857 and can swing as low as approximately 0.1V. Voltages below 0.5V on VAO will disable the MOSDRV output and force the IGDRV1 and IGDRV2 outputs to a zero overlap condition.

**CRMS:** A capacitor is connected between CRMS and ground to average the AC line voltage over a half cycle. CRMS is internally connected to the RMS detection circuitry.

**CT:** A capacitor (low ESR, ESL) is tied between CT and ground to set the ramp generator switching frequency in conjunction with RT. The ramp generator frequency is approximately given by:

$$f_{SW} \approx \frac{0.67}{R_T \bullet C_T}.$$

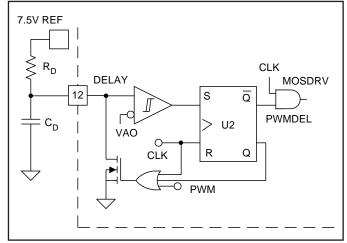

**DELAY:** A resistor to VREF and a capacitor to AGND are connected to DELAY to set the overlap delay time for the MOSDRV output stage. The overlap delay function can be disabled by removing the capacitor to AGND.

**IAC:** A resistor is connected to the rectified AC input line voltage from IAC. This provides the internal multiplier and the RMS detector with instantaneous line voltage information.

**IGDRV1:** Driver output for one of the two external IGBT power switches.

**IGDRV2:** Driver output for one of the two external IGBT power switches.

**MOSDRV:** Driver output for the external power MOSFET switch.

**MOUT:** Output of the analog multiply and divide circuit. The output current from MOUT is fed into a resistor to the return leg of the input bridge. The resultant waveform forms the sine reference for the current error amplifier.

**PKLMT:** Inverting input of the peak current limit comparator. The threshold for this comparator is nominally set to 0V. The peak limit comparator terminates the MOSDRV, IGDRV1 and IGDRV2 outputs when tripped.

**PGND:** Return for all high level currents, internally tied to the output driver stages of the UCC3857.

RT: A resistor, R<sub>T</sub> is tied between RT and ground to set the charging current for the internal ramp generator. The UCC3857 provides a temperature compensated 3.0V at RT. The oscillator charging current is therefore:  $3.0V/R_T$ . Current out of RT should be limited to  $250\mu A$  for best performance.

**VA-:** This is the feedback input for the outer voltage control loop. An external opto isolator circuit provides the

### PIN DESCRIPTIONS (continued)

output voltage regulation information to VA- across the isolation barrier.

**SS:** A capacitor is connected between SS and GND to provide the UCC3857 soft start feature. The voltage on VAO, is clamped to approximately the same voltage as SS. An internal  $10\mu$ A (nominal) current source is provided by the UCC3857 to charge the soft start capacitor.

**VD:** Positive supply rail for the three output driver stages. The voltage applied to VD must be limited to less than 18VDC. VD should be bypassed to PGND with a  $0.1\mu F$  to  $1.0\mu F$  low ESR, ESL capacitor for best results. VD and

VIN can be isolated from each other with an RC lowpass filter for better supply noise rejection.

**VIN:** Input voltage supply to the UCC3857. This voltage must be limited to less than 18VDC. The UCC3857 is enabled when the voltage on VIN exceeds 13.75V (nominal).

VREF: Output of the precision 7.5V reference. A  $0.01\mu F$  to  $0.1\mu F$  low ESR, ESL bypass capacitor is recommended between VREF and AGND for best performance.

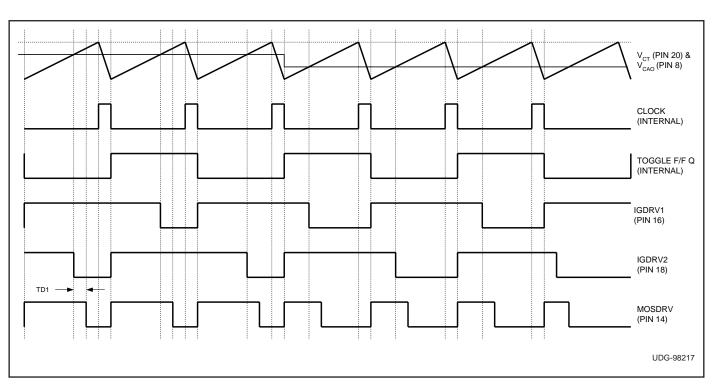

Figure 1. Typical control circuit timing diagram.

#### APPLICATION INFORMATION

UCC3857 is designed to provide a solution for single stage power factor correction and step-down or step-up function, using an isolated boost converter. The Typical Application Circuit shows the implementation of a typical isolated boost converter using IGBTs as main switches in push-pull configuration and using a MOSFET as an auxiliary switch to accomplish soft-switching of IGBTs. Many variations of this implementation are possible including bridge-type circuits. The presense of low frequency ripple on the output makes this approach practical for distributed bus applications. It will not provide the highly regulated low ripple outputs typically required by logic level supplies.

The circuit shown in the Typical Application Circuit provides several advantages over a more conventional approach of deriving a DC bus voltage from AC line with power factor correction. The conventional approach uses two power conversion stages and has higher cost and complexity. With the use of UCC3857, the dual functionality of power factor correction and voltage step-down is combined into a single stage.

The power stage comprises a current-fed push-pull converter where the ON times of the push-pull switches (Q1 and Q2) are overlapped to provide effective duty cycle of a conventional PWM boost converter. When only one switch is on, the power is transferred to the output

### **APPLICATION INFORMATION (continued)**

#### **BLOCK DIAGRAM**

through the transformer and the output rectifier. It can be seen that the \*\*, \*\* operation on the primary side of the circuit is that of a boost converter and UCC3857 provides input current programming using average current mode control to achieve unity power factor. The transformer turns ratio can be used to get the required level of output voltage (higher or lower than the peak line voltage). The transformer also provides galvanic isolation for the output voltage.

Power stage optimization involves design and selection of components to meet the performance and cost objectives. These include the power switches, transformer and inductor design.

The choice of IGBTs is based on their advantage over MOSFETs at higher voltages. For universal line operation, the voltage stress on the push-pull switches can approach 1000V. However, the slow turn-off of IGBTs can contribute high switching losses and the use of MOSFET (QA) helps turn the IGBTs off with zero voltage across them (ZCS turn-off). This is accomplished by keeping QA on (beyond the turn-off of Q1 or Q2 – see Fig. 1 for waveforms) to allow the inductor current to divert from IGBT to MOSFET while the IGBT is turning off and still maintain zero volts. The MOSFET delay time

(TD1) effectively adds to the boost inductor charge period. The voltage stress of the MOSFET is half the stress of the IGBTs under normal operating conditions. However, QA can see much higher voltage stress under start-up and short circuit conditions as the converter operates in a flyback mode then. For different operating requirements or constraints (e.g. single North American line operation), the choice of switching components may be different (e.g. MOSFETs for Q1 and Q2 and no QA) as the voltage stress is different. In that case, UCC3857 can still be used without using the MOSDRV output.

Transformer design is very critical in this topology. The push-pull transformer must have minimal leakage inductance between the primary and secondary windings. Similarly, the leakage between the two primary windings must be minimized. In practice, it is hard to achieve both targets without using sophisticated construction techniques such as interleaving, use of foils etc. In many cases, it may be beneficial to use a planar transformer to achieve these objectives. The effects of higher leakage inductance include higher voltage stresses, ringing, power losses and loss of available duty cycle. The high voltage levels make it difficult to design effective snubber circuits for this leakage induced ringing.

### **APPLICATION INFORMATION (cont.)**

The design of the boost inductor is very similar to the conventional boost converter. However, as shown in the Typical Application Circuit, an additional winding connected to the output through a diode is required on the boost inductor. This winding must have the same turns ratio as the transformer and meet the isolation requirements. This winding is required to provide a discharge path for the inductor energy when the push-pull switches are both off. During start-up, when the output voltage is zero, the converter can see very high inrush currents. The overcurrent protection circuit of UCC3857 will shut down all the outputs when the set threshold is crossed. At that instance, the boost inductor auxiliary winding directs the energy to the output. This is a preferred manner of bringing the output voltage up to prevent the main switches from handling the high levels of inrush current. However, when the auxiliary winding is transferring the power to the output, the voltage stress across QA becomes input voltage plus the reflected output voltage-higher than its steady state value of reflected output voltage.

#### Chip Bias Supply and Start-up

UCC3857 is implemented using Unitrode's BCDMOS process which allows minimization of the start-up (60 A typical) and operating (3.5mA typical) supply currents. It results in significantly lower power consumption in the trickle charge resistor used to start-up the IC.

#### **Oscillator Set-up**

The oscillator of UCC3857 is designed to have a wide ramp amplitude (4.5V p-p) for higher noise immunity. The CT pin has the sawtooth waveshape and during the discharge time of  $C_T$ , a clock pulse is generated. During the discharge period, the effective internal impedance to GND is 600 . Based on this, the discharge time is given by 831 $\bullet$ C<sub>T</sub>. As shown in the waveforms of Fig. 1, the internal clock pulse width is equal to the discharge time and that sets the minimum dead time between IGDRV1 and IGDRV2. The clock frequency is given by

$$f_{SW} = \frac{1}{(1.5 \bullet R_T + 831) \bullet C_T} \approx \frac{1}{(1.5 \bullet R_T \bullet C_T)} \tag{1}$$

The IGDRV1 and IGDRV2 outputs are switched at half the clock frequency while MOSDRV is switched at the clock frequency.

#### Reference Signal (I<sub>MULT</sub>) generation

Like the UC3854 series, the UCC3857 has an analog computation unit (ACU) which generates a reference current signal for the current error amplifier. The inputs to the ACU are signals proportional to instantaneous line voltage, input voltage RMS information and the voltage

error amplifier output. Unlike prior techniques of RMS voltage sensing, UCC3857 employs a patent pending technique to simplify the RMS voltage generation and eliminate performance degradation caused by the previous techniques. With the novel technique (shown in Fig. 3), need for external 2-pole filter for  $V_{RMS}$  generation is eliminated. Instead, the IAC current is mirrored and used to charge an external capacitor ( $C_{CRMS}$ ) during a half cycle. The voltage on CRMS takes the integrated sinusoidal shape and is given by equation 2. At the end of the half-cycle, CRMS voltage is held and converted into a 6-bit digital word for further processing in the ACU.  $C_{CRMS}$  is discharged and readied for integration during next half cycle.

The advantage of this method is that the second harmonic ripple on the  $V_{RMS}$  signal is virtually eliminated. Such second harmonic ripple is unavoidable with the limited roll-off of a conventional 2-pole filter and results in 3rd harmonic distortion in the input current signal. The dynamic response to the input line variations is also improved as a new  $V_{RMS}$  signal is generated every cycle.

$$V_{CRMS} = \frac{I_{AC}(pk)}{2 \cdot \omega \cdot C_{CRMS}} (1 - \cos \omega t)$$

(2)

$$V_{CRMS}(pk) = \frac{I_{AC}(pk)}{\omega \cdot C_{CRMS}}$$

(2a)

For proper operation,  $I_{AC}(pk)$  should be selected to be 100 A at peak line voltage. For universal input voltage with peak value of 265 VAC, this means  $R_{AC}=3.6M$ . The noise sensitivity of the IC requires a small bypass capacitor for high frequency noise filtering. The value of this capacitor should be limited to 220nF maximum. The  $V_{CRMS}$  value should be approximately 1V at the peak of low line (80 VAC) to minimize any digitization errors. The peak value of  $V_{CRMS}$  at high line then becomes 3.5V. The desired  $C_{CRMS}$  can be calculated from equation 2 to be 75nF for 60Hz line.

The multiplier output current is given by equation (3) with K = 0.33.

$$I_{MULT} = \frac{(V_{VAO} - 0.5) \bullet I_{AC} \bullet K}{V_{CRMS}^2}$$

(3)

The multiplier peak current is limited to 200 A and the selected values for  $I_{AC}$  and  $V_{CRMS}$  should ensure that the current is within this range. Another limitation of the multiplier is that  $I_{MULT}$  can not exceed two times the IAC current, limiting the minimum voltage on  $V_{CRMS}$ .

The discrete nature of the RMS voltage feedforward means that there are regions of operation where the in-

# **APPLICATION INFORMATION (cont.)**

Figure 3. Novel RMS voltage generation scheme.

put voltage changes, but the  $V_{RMS}$  value fed into the multiplier does not change. The voltage error amplifier compensates for this by changing its output to maintain the required multiplier output current. When the output of the ADC changes, there is a jump in the output of the error amplifier. This has minimal impact on the overall converter operation.

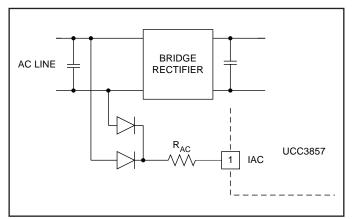

Another key consideration with the RMS voltage scheme is that it relies on the zero-crossing of the lac signal to be effective. At very light loads and high line conditions, the rectified AC does not quite reach zero if a large capacitor is being used for filtering on the rectified side of the

Figure 4. Alternative implementation for sensing I<sub>AC</sub>.

bridge. In such instances, the feedforward effect does not take place and the controller functionality is compromised. For UCC3857, the  $I_{AC}$  current should go below 10 A for the zero crossing detection to take place. It is recommended that the capacitor value be kept low enough for light load operation or that the alternative scheme shown in Fig. 4 be used for  $I_{AC}$  sense.

#### **Gate Drive Considerations**

The gate drive circuits in UCC3857 are designed for high speed driving of the power switches. Each drive circuit consists of low impedance pull-up and pull-down DMOS output stages. The UCC3857 provides separate supply and ground pins (VD and PGND) for the driver stages. These pins allow better local bypassing of the driver circuits. VD can also be used to ensure that the SOA limits of the output stages are not violated when driving high peak current levels. For this, VD can be kept as low as possible (e.g. 10V) while VIN can go higher to handle the UVLO requirements.

#### **Current Amplifier Set-up**

Once the multiplier is set-up by choosing the  $V_{RMS}$  range, the current amplifier components can be designed. The maximum multiplier output is at low line, full load conditions. The inductor peak current also occurs at the same point. The multiplier terminating resistor can be determined using equation 4.

$$R_{MULT} = \frac{I_{L-PK} \bullet R_{SENSE}}{I_{MULT-PK}} \tag{4}$$

The current amplifier can be compensated using a previously presented techniques (U-134) summarized here. A simplified high frequency model for inductor current to duty cycle transfer function is given by

$$G_{id}(s) = \frac{\dot{i}_L}{\dot{A}} = \frac{Vo}{sL} \tag{5}$$

The gain of the current feedback path at the frequency of interest (crossover) is given by

$$\frac{\dot{d}}{\dot{i_L}} = R_{SENSE} \bullet \frac{R_Z}{R_I} \bullet \frac{1}{V_{SE}}$$

(6)

Where VSE is the ramp amplitude (p-p) which is 4.5V for UCC3857. Combining equations. 5 and 6 yields the loop gain of the current loop and equating it to 1 at the desired crossover frequency can result in a design value for  $R_Z$ . The current loop crossover frequency should be limited to about 1/3 of the switching frequency of the converter to ensure stability. See Unitrode Application Note U-140 for further information.

#### **Trailing Edge Delay**

As shown in the waveforms of Fig. 1, the modified isolated boost converter requires drive signals for the two main (IGBT) switches and the auxiliary (MOSFET) switch with certain timing relationships. The delay between turn-off of an IGBT and turn-off of the MOSFET can be programmed for the UCC1857. In a PFC application, the input line varies from zero to the AC peak level, resulting in a wide range of required duty ratios. A fixed delay time will induce line current distortion at the peaks of the AC line under high line and/or light load conditions. This is caused by the minimum controllable duty ratio imposed on the modulator by the fixed delay. If the minimum controllable duty ratio is fixed, the inner current loop can exhibit a limit cycle oscillation at the line peaks, inducing line current distortion.

The UCC1857 has an adaptive MOSFET delay generator, which is directly modulated by load power demand. Referring to Fig. 5, this circuit directly varies the delay time based on the output level of the voltage error amplifier, which in an average current mode PFC converter

with line feedforward is indicative of load power. The delay time is programmed with external components,  $R_D$  and  $C_D$ . The sequence of events starts when the internal CLK signal resets latch U2, causing PWMDEL to go high and the Q output to go low.  $C_D$  was discharged via M1 and is held low until the internal PWM signal goes low (indicating turn-off of either of the IGBT drives). At this point M1 turns off and  $C_D$  charges towards the 7.5V reference through  $R_D$ . A comparator U1 compares this voltage to the voltage error amplifier output ( $V_{VAO}$ ). When the voltage on  $C_D$  is greater than  $V_{VAO}$ , the latch U2 is set causing PWMDEL to go low. PWMDEL is logically

Figure 5. Circuit for adaptive MOSFET delay generation.

ANDed with CLK to produce the signal which commands the MOSFET driver output (MOSDRV). The delay time, TD1, is given by

$$TD1 = -R_D \bullet C_D \bullet \ell n \left( \frac{7.5 - V_{VAO}}{7.5} \right)$$

(7)

This technique reduces the overlap delay at light loads or high lines, but maintains a longer delay when the line voltage is low or the load is heavy. This by definition reduces the minimum controllable duty ratio to an acceptable level, and is programmable by the user. Reducing the delay time under light current conditions is acceptable since the IGBT current is directly proportional to load current. By providing programming flexibility with  $R_D$  and  $C_D$ , the delay times can be optimized for current and future classes of IGBT switches. The delay can also be set to zero by removing  $C_D$  from the circuit.

#### PACKAGE OPTION ADDENDUM

18-Sep-2008

#### PACKAGING INFORMATION

www ti com

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| UCC3857DW        | OBSOLETE              | SOIC            | DW                 | 20                  | TBD                     | Call TI          | Call TI                      |

| UCC3857DWTR      | OBSOLETE              | SOIC            | DW                 | 20                  | TBD                     | Call TI          | Call TI                      |

| UCC3857N         | OBSOLETE              | PDIP            | N                  | 20                  | TBD                     | Call TI          | Call TI                      |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated